学习内容

第一章看一看 PPT 过一遍即可,一些概念性的记一下,可能出个填空题啥的

第二章看书+PPT

汇编部分第三章 PPT+书一起看,PPT 上有一些题目看一下,然后就是书上有一些伪指令是 PPT 里没有的可以看看

第四章内存部分应该会考一个硬件分析让你写出地址空间啥的,这块看看 PPT 然后书上再选两题看看,书里都有解析,还有前年试卷的分析题也是这种类型,今年期末考也考了

接口部分 PPT 的章节和书的章节是不一样的,根据 PPT 里的芯片名字去目录里找对应的章节看,咱们学习的是 8259,8255,0832,0809,8237,8255,8251,8253 这几个芯片,还有这一块 PPT 里有个中断的部分,也要看一下

有不懂的地方可以去找慕课看一下,也可以随时问我

考试重点

不知道题型与期末考一不一样,但是重点应该是一样的,选择题、填空题、判断题、简答题这种也没法预测,只能自己看 PPT 和书的时候多注意一下,这几种题型可以看看何燕平老师的 2017 复习 PPT,大概整体复习完一遍后,去做一做前年的试题

选择题(举例)

PC 里放的是啥

中断向量、中断向量表、中断入口程序地址

…

填空题(举例)

给你一条指令,问寻址方式

中断的分类

…

判断题

简答题(举例)

这个也不太好说他会出什么,说不定 ppt 里不在意的地方他就出了…,比如接口的功能、中断的分类…

字节对齐问题

MOV AX,[2000H]与MOV AX,[2001H]的区别8086 采用的编址方式,这种编址方式有什么优点/缺点

结合 8259 内部结构,描述中断源如何向 8259 提出申请,8259 如何判优等等类似的问你一个芯片的工作过程这样

给一段汇编伪指令,画出内存空间(课本第三章那块有)

中断响应过程

搞个宏展开

…

计算题

波特率的计算(应该必考)

注意一帧要包括起始位、有效位、奇偶校验位、停止位,题目可能只告诉你几位有效位、几位停止位,采用奇校验还是偶校验,计算的时候要记得加上 1 位起始位。

波特率、波特率因子与发送/接收时钟频率的关系

$发送/接收时钟频率(Hz) = 波特率(bps)*波特率因子$

分析题

硬件分析

存储器扩展 [例题见第四章 PPT 第 17 页、前年考卷分析题](应该必考)

给你一个图,让你写出内存地址范围,问是否存在地址重叠

软件分析

给你一段代码,问你运行结果、各存储器的变化之类的,这里要注意隐含的变化,比如出栈入栈时 SP 的变化、串操作指令中 SI、DI 的变化、各个指令对标志位的影响等等

设计题

汇编编程部分(难度应该和实验难度差不多)

写出程序的一部分/子程序

跳转、循环、排序、比较、递归、累加、阶乘…

显示 16 进制数/字符/字符串/…

从键盘键入字符串(21H 各号功能)

从键盘接受一个 16 位/10 位的数…

写出一个完整的汇编程序

注意:

子程序要有 ret

对于某些指令注意指明操作数的位数,如

MOV BYTE PTR [DI],0FFH注意题目要求,要的是字还是字节操作

若要编写完整程序,要注意伪指令的完整结构,包括常用的伪指令、段的定义、程序开始和结束(4C00H)等

对于字符串处理指令,用之前别忘了设置 DF

接口

8255重点,接数码管/小键盘,可以看看书上(我记得好像是有代码的)、实验代码,顺便一般都是方式 0 工作

注意就算到时候写不出来,也不要空着,至少要能写出 A 口、B 口、C 口、控制口的端口地址,控制字初始化也得会写,设置内存起始地址啊之类的,总之能写多少就写多少

0809/0832 可能会考一个,这两个看看 PPT,一步一步写,至少写出端口、通道地址

8259重点,同样的,就算写不出来,也要能写多少写多少,至少会写端口地址、控制字的初始化

8259 也可能出成简答之类,问你只有两个端口,那它是怎么初始化的,怎么知道是写哪个命令字啊

[奇偶地址、顺序、特征位]

也可能让你算个中断向量啊啥的

8251 一般放计算题里考波特率计算

8253,这个它的工作模式确实有点多…其实我自己也记不住,不过期末考的时候考了,能看看记记就记记… …

8237

汇编常用

21H 中断

4CH 号功能:结束程序

MOV AX, 4C00H

02H 号功能:在屏幕上显示字符

MOV DL, ‘A’

MOV AH, 02H01H 号功能:由键盘输入一个字符

0A 号功能:由键盘输入字符串

调用之前先设置好缓冲区,第一个字节事先填入最多允许接受的字符个数(包括 0DH),第二个字节留空,本功能自动回填实际输入的字符个数(不包括回车符),第三个字节起存放实际的字符串,用户按回车结束,从而最后一个字符是 0DH,若用户输入字符超过设置,不予响应

调用参数:DS:DX=缓冲区首地址 DS:[DX]=缓冲区最大容量

返回参数:DS:[DX+1]=实际输入字符数 DS:DX+2=字符串首地址

常用 ASCII 码

回车 0DH

换行 0AH

终结符 ‘$’

编程框架

框架(简略模式)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21;采用简化版的段定义伪指令,下一个段的开始即表示上一个段的结束

.model small

.stack [常量(大小为常量个字节)默认1KB]

.data

; ...定义的数据

; [变量名] DB 操作数列表

; DB(define word)

; DD(define double word)

; DQ

; DT

; PORTA EQU 20H 符号常量也可用=定义

; PTR 类型属性操作符 转换类型 类型 PTR 变量名/含变量名的表达式

.code [段名]

start: mov ax, @data ; @data表示代码段名

mov ds, ax ; 装载数据段

; ....一些操作

mov ax,4c00h

int 21h ; 调用21号中断结束汇编

end start框架(非简略模式)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20SSTACK SEGMEN STACK

DB 200 DUP(0)

SSTACK ENDS

DATA SEGMENT

; ORG 3000H ; ORG规定起始地址

; ARY DB 100,98,-1,-2,-4,7,0,100,32,1

; ARRY DQ DUP(?) ; DUP复制操作符,?表示只分配存储空间

DATA ENDS

CODE SEGMENT

ASSUME CS:CODE,DS:DATA,SS:SSTACK

START: MOV AX,DATA

MOV DS,AX

MOV AX,STACK

MOV SS,AX

; CS不需要送段寄存器

; ...一些操作

MOV AX,4C00H

INT 21H ; 调用21号中断结束汇编

CODE ENDS

END START

其它

标志寄存器 (记)

16 位(9 位有效,7 位空闲)

CF、DF、IF、TF 可由指令设置,其余 5 个由 EU 设置

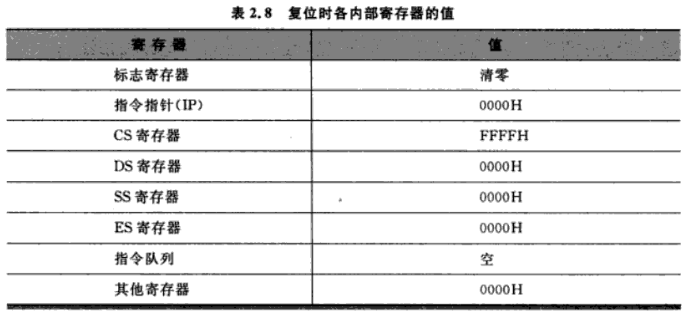

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OF DF IF TF SF ZF AF PF CF 复位后寄存器状态

注意 CS 复位后值为 0FFFFH

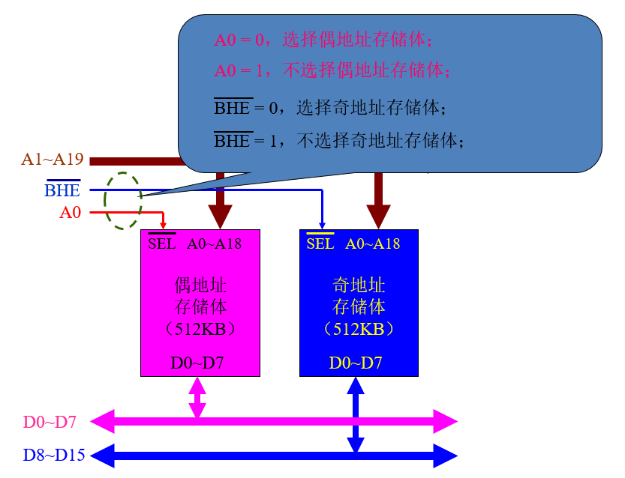

关于字节对齐问题

从偶地址单元开始读/写一个字,需要一个总线周期

$\overline{BHE}$ $A_0$ 操作 所用数据线 0 0 从偶地址单元读/写两个字节 $D_0$~ $D_{15}$ 1 0 从偶地址单元读/写一个字节 $D_0$~$D_{7}$ 0 1 从奇地址单元读/写一个字节 $D_8$~$D_{15}$ 从奇地址单元开始读/写一个字,需要两个总线周期

$\overline{BHE}$ $A_0$ 操作 所用数据线 0 1 第一步:从奇地址单元读/写一个字节 $D_8$~$D_{15}$ 1 0 第二步:从偶地址单元读/写一个字节 $D_0$~$D_{7}$ 关于 IP、CS 的出栈入栈顺序

可以这么记,栈是向下生长的(地址由大到小),在栈中,保存段地址的地址总是大于保存段内偏移地址的地址

OFFSET 和 LEA 的区别

OFFSET 是在编译的时候就计算出偏移结果,实际运行程序的时候已经被替换为一个数值了,而 LEA 是在运行的时候才执行

暂时想到这些,以后想到再补充吧