2.1 8086CPU 的编程结构

16 根地址线、20 根数据线、时钟频率 5MHz

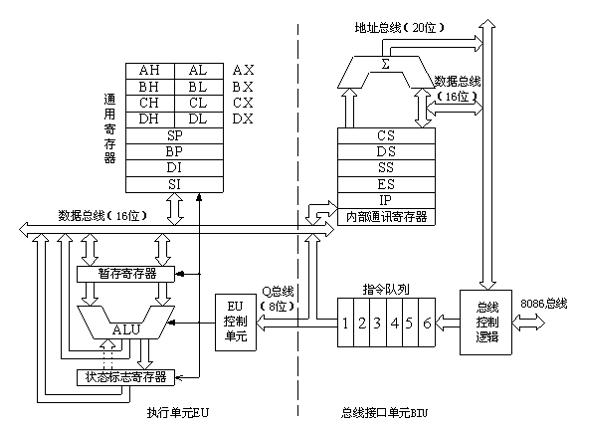

8086 分为总线接口单元(BIU)和执行单元(EU)

执行单元包括:

通用寄存器

8 个 16 位寄存器

4 个通用寄存器:AX、BX、CX、DX

可以拆分为 2 个单独的 8 位寄存器

AX 累加器

I/O 指令必用

BX 基址寄存器

存放基地址

CX 计数寄存器

循环指令和串处理隐含的指定计数器

DX 数据寄存器

可与 AX 拼接成 32 位,DX 中存放高 16 位

I/O 指令中存放外设端口号

4 个通用寄存器:SP、BP、SI、DI,更多被用于变址寻址:SI/DI 与段寄存器 DS/ES 联用实现数据的寻址;SP、BP 用于堆栈操作,与 SS 联用实现寻址

SI 源变址寄存器

间接寻址时用作地址寄存器和变址寄存器

串操作时用作源变址寄存器

DI 目的变址寄存器

间接寻址时用作地址寄存器和变址寄存器

串操作时用作目的变址寄存器

SP 堆栈指针寄存器

BP 基址指针寄存器

标志寄存器 (记)

16 位(9 位有效,7 位空闲)

CF、DF、IF、TF 可由指令设置,其余 5 个由 EU 设置

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OF DF IF TF SF ZF AF PF CF 状态位

(1) CF (Carry Flag)

进位标志,反应算术运算后最高位(字节操作 $D_7$,字操作 $D_{15}$)是否出现进位/借位,有进位则为1。

主要用于加减法,移位和环移指令也会改变 CF

(2) PF (Parity Flag)

奇偶标志,1表示结果中有偶数个 1,0表示结果中有奇数个 1

(3) AF (Auxiliary Carry Flag)

辅助进位标志,1表示 $D_3$向 $D_4$进位/借位,0表示没有

用于 BCD 码算术运算指令

(4) ZF (Zero Flag)

零标志,1标志运算结果为 0

(5) SF (Sign Flag)

符号标志,与带符号运算的结果符号位($D_7/D_{15}$)一致,1表示结果为负数

(6) OF (Overflow Flag)

溢出标志,带符号数(补码)运算结果是否超过机器能表示的范围($-128\sim 127 / -32768\sim 32767$),1表示溢出

控制位

(1) DF (Direction Flag)

方向标志,字符串操作时用到,字节操作加减 1,字操作加减 2

1表示递减,即高地址向低地址

0表示递增,即低地址向高地址

(2) IF (Interrupt Enable Flag)

中断允许标志,1表示允许响应

IF 对不可屏蔽中断请求及内部中断无效

(3) TF (Trap Flag)

陷阱标志,为1时每执行完一条指令都自动产生一个内部中断,常用于调试

算术逻辑单元(ALU)

EU 控制系统

总线接口单元包括:

段寄存器

机器字长=存储字长=16 位

小端存储,即高字节存放在高地址,低字节存放在低地址,以低字节的地址作为整个字(双字)的地址

8086 的分段管理:物理地址=(段寄存器)*16+(地址寄存器)

段与段之间可以是连续的、断开的、部分重叠或全部重叠的

分段管理的意义:减少指令长度,缩短指令执行时间;便于程序浮动装配

一些默认行为:

取指令时:CS:IP

堆栈操作时:SS:SP

涉及存储器操作数时(除了以 BP 为地址寄存器外):DS 作为默认段基址(可替换为 CS/DS/ES,添加段跨越前缀)

偏移地址为某 16 位偏移量(可以是指令中直接提供的 16 位地址、某个 16 位寄存器(BX/DI/SI)中的值、指令中的位移量加上某 16 位地址寄存器(BX/BP/DI/SI)中的值)

ES 用于串操作指令中的数据块传送指令:

源地址:默认 DS 段基址(可替换为 CS/DS/ES,添加段跨越前缀),偏移地址 SI

目的地址:ES:DI

BP 作地址寄存器:

SS 默认段基址(可替换为 CS/DS/ES,添加段跨越前缀),SS:EA

4 个段寄存器

- 代码段寄存器 CS

- 数据段寄存器 DS

- 附加段寄存器 ES

- 堆栈段寄存器 SS(后进先出)

指令指针寄存器 IP(就是计组里说的 PC)

提供下一条指令的地址,具体来说是下一条指令的(代码)段内偏移地址,代码段的段地址由 CS 提供

地址形成逻辑(20 位地址加法器形成地址)

总线控制逻辑

指令队列(6 字节指令队列,先进先出,存放待执行指令,出去的进入 IP)

2.2 8086CPU 的工作模式与引脚功能

工作模式(略)

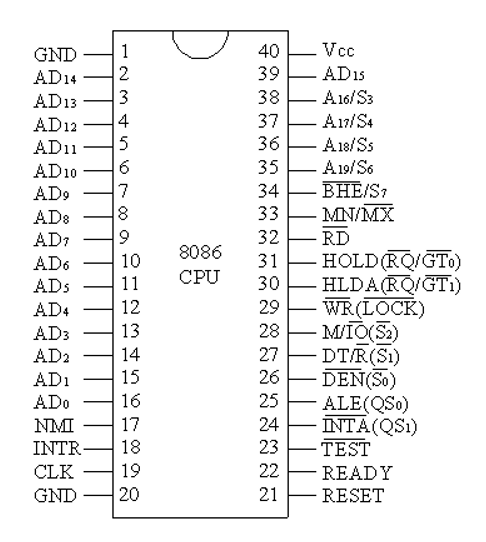

引脚功能

注: /分时复用 (最大模式/最小模式)

最小模式:

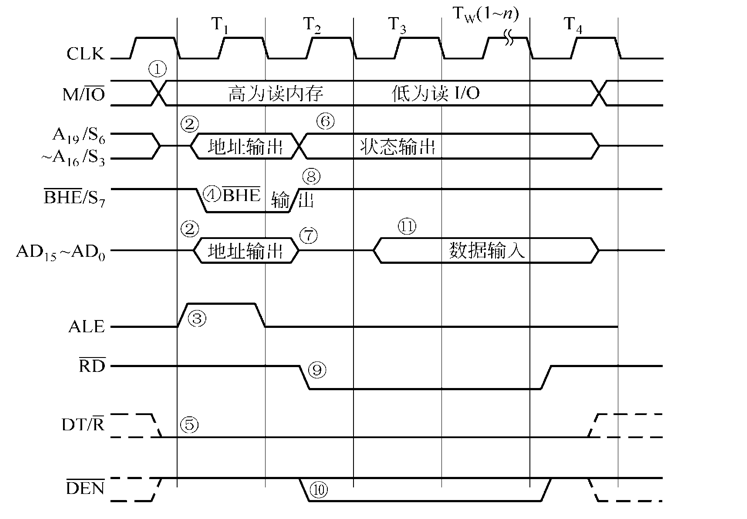

$AD_0~AD_{15}$:地址/数据分时复用(双向、三态)

$T_1$时用作地址总线的低 16 位,其余时间用作数据总线进行数据传输

$AD_{16}/S_3 \sim AD_{19}/S_6$:地址总线高 4 位/状态总线(输出、三态)

$T_1$时用作地址总线的高 4 位(I/O 操作中置0),其余时间表示 CPU 的状态信息

$S_6$恒为低电平,$S_5$反映 IF 的值,$S_4$和 $S_3$表示正在使用的段寄存器

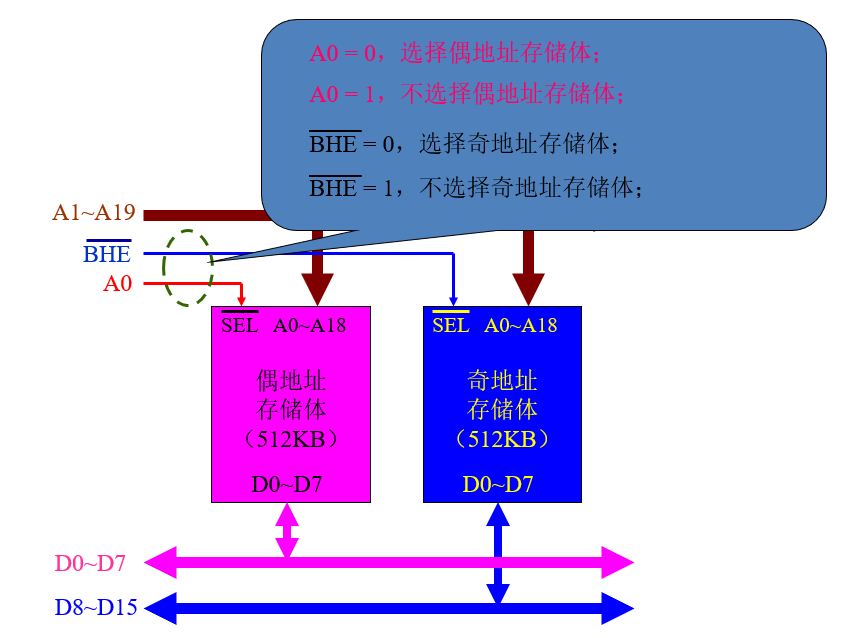

$\overline{BHE}/S_7$:高 8 位数据总线允许/状态信号(输出)

$T_1$时作为总线高半部分允许信号,低电平有效,其余时间输出状态信号 $S_7$;DMA 方式下为高阻态

与 $A_0$结合决定高字节工作还是低字节工作(见奇地址存储与偶地址存储,估计大概率考)

CLK:系统时钟信号(输入)

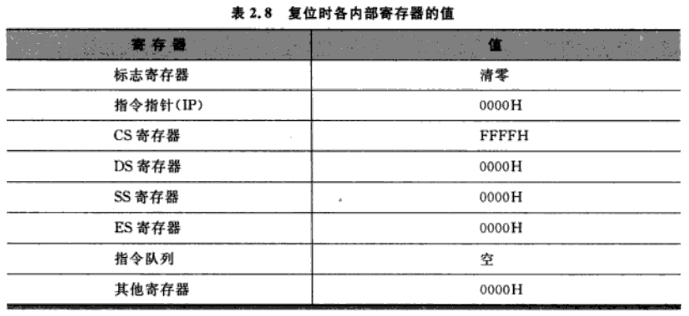

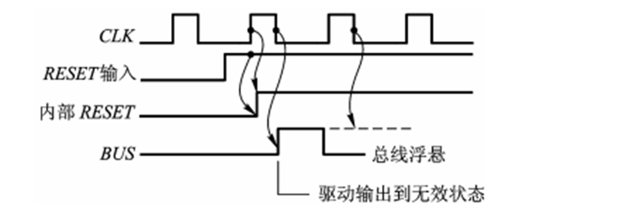

RESET:复位信号(输入)

至少维持 4 个时钟周期的高电平才有效,复位后各寄存器状态如下图所示:

注意 CS 寄存器复位后的值是 0FFFFH

IF 也被清零辽,系统关中断

当复位信号变为低电平时,CPU 从 FFFF0H 处开始执行程序,该处通常存放一条 JMP 指令,以转移到系统程序的实际开始处。复位时地址总线浮空,直到 cpu 脱离复位状态;其他控制信号先变高一段时间,然后浮空;ALE、HLDA 信号变为无效

复位信号 RESET 撤销后,经过 7 个时钟周期,CPU 才启动

NMI:不可屏蔽中断请求信号(输入)

上升沿触发,8086 完成当前指令后跳转到不可屏蔽中断服务程序

INTR:可屏蔽中断请求信号(输入)

电平触发,每条指令的最后一个时钟周期 CPU 采样该信号,若 INTR 为高电平且 IF=1,则执行中断响应;若 IF=0 则不响应,可见 INTR 可由软件复位 IF 加以屏蔽

READY:准备就绪信号(输入)

当被访问部件无法在规定时间完成数据传输,就向 CPU 发 READY 为低电平的信号,这样 CPU 就插入若干个等待周期 T

w,完成传输后被访问部件再使 READY 信号为高电平$\overline{RD}$:读控制信号(三态、输出)

低电平时 CPU 执行读操作;DMA 方式下为高阻态

$\overline{TEST}$:等待测试控制信号(输入)

WAIT 指令期间,每隔 5 个时钟周期 CPU 对该引脚采样,高电平继续等待,低电平继续执行后续指令

MN/$\overline{MX}$:最小/最大模式控制信号(输入)

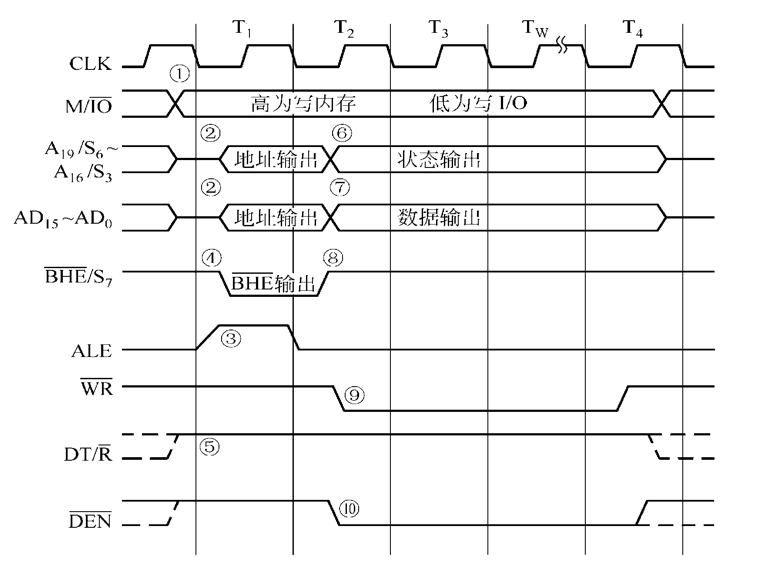

M/$\overline{IO}$:存储器/IO 访问控制信号(输出)

ALE:地址锁存允许信号(输出)

高电平有效,总线周期的第一个时钟周期内发出正脉冲信号,其下降沿将 $AD_0\sim AD_{15}$ 以及 $AD_{16}/S_3\sim AD_{19}/S_6$上的地址信息锁存进地址锁存器

$\overline{DEN}$:数据允许信号(输出、三态)

用作总线收发器的允许控制信号,在 CPU 访存或 I/O 的总线周期的后一段时间内有效

DT/$\overline{R}$:数据发送/接受信号(输出、三态)

CPU 写/读

$\overline{WR}$:写控制信号(输出、三态)

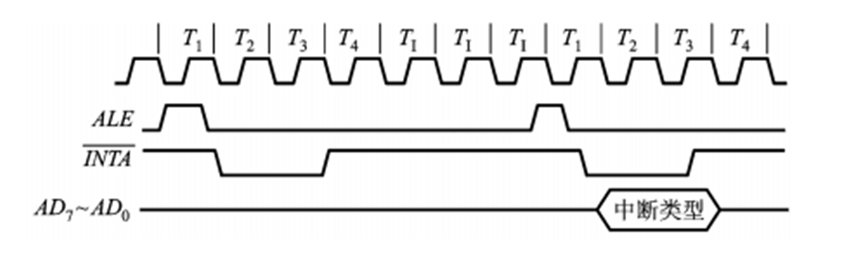

$\overline{INTA}$:中断响应信号(输出、三态)

当 CPU 响应 INTR 的可屏蔽中断请求时,$\overline{INTA}$在中断响应周期内变为低电平

HOLD:保持请求信号(输入)

高电平时 CPU 完成当前总线周期后进入 HOLD 状态,让出总线控制权

HLDA:保持响应信号(输出)

CPU 对 HOLD 信号的响应信号,使三态信号线全部处于高阻态,外部逻辑控制总线

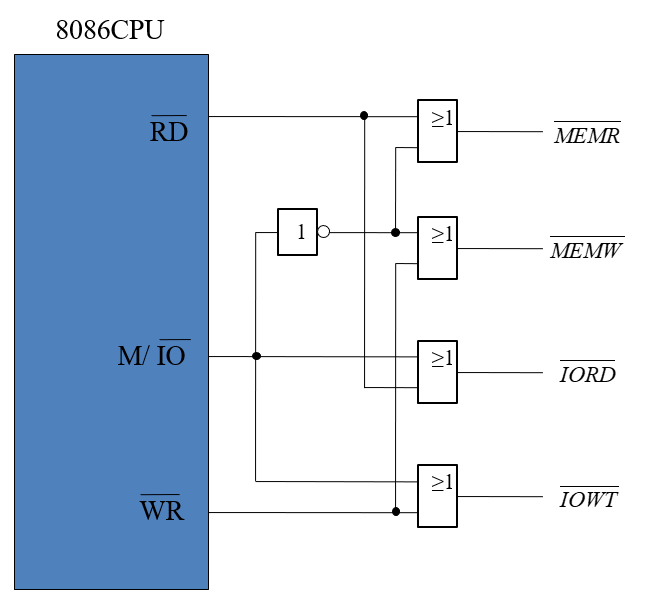

存储器和 I/O 端口的读写控制信号逻辑

$\overline{RD}$ $M/\overline{IO}$ $\overline{WR}$ 操作 0 1 1 读内存 0 0 1 读外设 1 1 0 写内存 1 0 0 写外设 注意与后面的 8237A 比较,8237A 作为主片时是同时读内存写外设/写内存读外设

2.3 8086CPU 的操作和时序

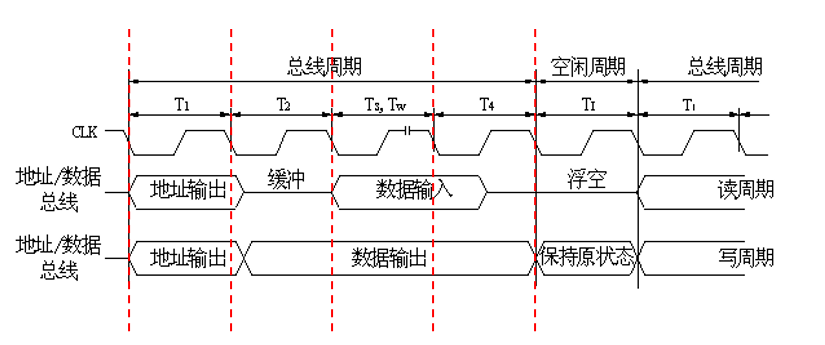

基本概念

机器周期:与主频相关,又叫时钟周期

指令周期:CPU 执行一条指令需要的时间,以机器周期为单位

总线周期:CPU 通过总线访问存储器或 I/O 设备的时间周期,以机器周期为单位

8086 的总线周期

缓冲:撤销地址信息,地址信息进地址锁存器

数据传输:允许插入若干个等待周期

8086 的操作类型

内部操作:ALU 操作、寄存器操作

外部操作:总线读/写操作、中断响应操作、中线保持/响应操作、系统复位/启动操作、暂停操作

8086 的操作时序(最小模式)

总线操作

总线读操作

总线写操作

中断响应操作

响应中断时 CPU 执行两个中断周期,第一个周期的 $T_2\sim T_4$ 时 $\overline{INTA}$为低电平,这里作为对中断请求设备的响应;第二个周期的 $T_2\sim T_4$ 时$\overline{INTA}$为低电平,这里用于通知中断请求设备(通过中断控制器)把中断类型号(决定了中断服务程序入口地址)送到数据线低八位($AD_7\sim AD_0$)。在 8086 中,2 个周期之间有 3 个空闲周期 $T_I$

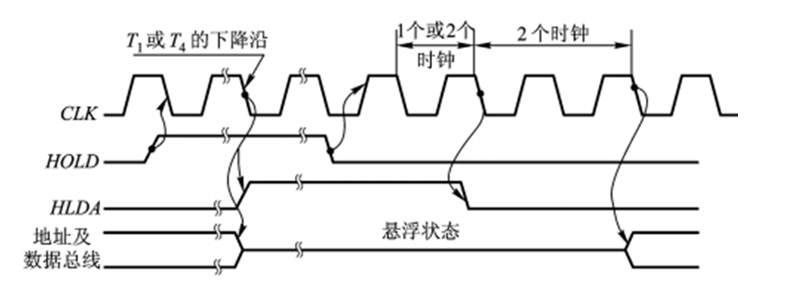

总线保持与响应操作

其他系统总线主设备向 8086 请求总线,发送 HOLD 请求信号,CPU 接收到 HOLD 信号后,在当前总线周期 $T_4$或空闲周期 $T_I$的后沿输出保持响应信号 HLDA,然后从下一个时钟开始让出总线控制权。外设的 DMA 传输结束后,使 HOLD 信号变为低电平,则下一个时钟的下降沿HLDA 信号变为低电平(无效) [HOLD 信号由外设驱动]

复位和启动操作

复位后的系统状态见RESET 信号

2.4 8086CPU 系统的存储器组织

小端存储,低字节在低地址单元,高字节在高地址单元

存储单元按字节组织,地址范围 00000H~FFFFFH

存储字(两个字节)采取边界对准(低字节存放在偶地址单元,高字节存放在奇地址单元)的规则存放

8086 通过低八位数据总线访问偶地址存储单元/IO 端口,通过高八位数据总线访问奇地址存储单元/IO 端口

从偶地址单元开始读/写一个字,需要一个总线周期

$\overline{BHE}$ $A_0$ 操作 所用数据线 0 0 从偶地址单元读/写两个字节 $D_0\sim D_{15}$ 1 0 从偶地址单元读/写一个字节 $D_0\sim D_7$ 0 1 从奇地址单元读/写一个字节 $D_8\sim D_{15}$ 从奇地址单元开始读/写一个字,需要两个总线周期

$\overline{BHE}$ $A_0$ 操作 所用数据线 0 1 第一步:从奇地址单元读/写一个字节 $D_8\sim D_{15}$ 1 0 第二步:从偶地址单元读/写一个字节 $D_0\sim D_7$

简答

8086 有哪几个通用寄存器?哪些提供了字节访问?

AX,累加器

BX,基址寄存器

CX,计数寄存器

DX,数据寄存器

SI,源变址寄存器

DI,目的变址寄存器

SP,堆栈指针寄存器

BP,基址指针寄存器

AX/BX/CX/DX 提供字节访问

标志寄存器各标志位的含义?IP 和 SP 的含义?

8086 有哪几个段寄存器?

寄存器和存储器的区别?

8086 的一个字(16 位)是如何存入存储器的?

8086 分为哪两个部分?它们如何协调工作?

8086 分为总线接口单元和执行单元,BIU 和 EU 是并行工作的,又是相互配合的,体现在:

当指令队列中有 2 个空字节时,BIU 就启动,将新指令送入队列

EU 在指令执行过程中,需要访问存储器或 I/O 时,向 BIU 发出请求

执行转移指令、调用指令以及返回指令时,指令队列自动清空

8086 复位后各寄存器的状态?

8086 使用存储器地址访问数据时,能根据地址确定数据的大小吗?

8086 的地址空间是多大?

1 个段的首地址的特点?

一个物理地址由段地址和偏移地址组成,这种表示是唯一的吗?

如何将段地址和偏移地址合成成物理地址?